Flip-Flops and Counters

Up until now, our digital circuits have been strictly combination -- they take inputs and react to them. While they are capable of complex calculations, they lack the ability to remember what they've done. This lack of memory severaly restricts the capabilities of the circuits we can design.

The flip-flop is the basic unit of digital memory. A flip-flop can remember one bit of data. Sets of flip-flops are called registers, and can hold bytes of data. Sets of registers are called memories, and can hold many thousands of bits, or more.

The basic flip-flop circuit is the classic set of cross-coupled NAND gates. Since nobody builds flip-flops from the gate level anymore, we'll skip past this level of analysis, and move straight into the chips we'll actually use. But if you're interested, The Art of Electronics devotes many pages to the inner workings of flip-flops, from the cross coupled NAND's on up.

- D-flops

One of the most common kinds of flip-flops (or, just flops) is the D-type flop. Like all flops, it has the ability to remember one bit of digital information. What makes the D-flop special is that it is a clocked flip-flop. We'll spend some time looking at what that means.

Here's the pin out of the 74HCT74N, a dual D-type flip-flop. Note that the 'dual' designation means that two flops come on one chip. |

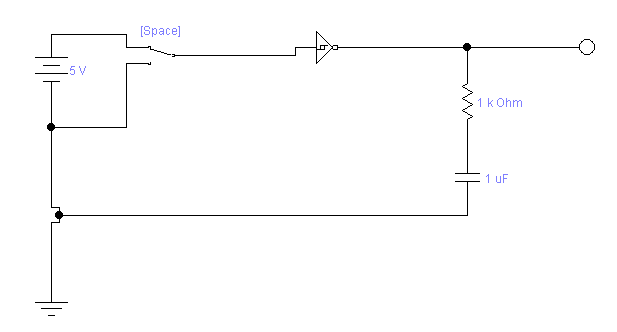

Having a component with memory can help us design circuits to solve a real variety of problems. To see how flexible flops are, we'll look at the problem of switch debounce.Consider this circuit, which is a fairly standard design for getting digital input from a push=button: We could get rid of the bounce by using a low-pass filter. However, this would slow down our response time, since we'd now have to allow for the RC curve. Instead, we'll feed the output of our physical switch into a D-flop, and clock the flop with regular pulses from a 555 timer.

1. First, set up a push button switch to deliver a logic level input. View its output on a scope, and look at the switch bounce. Measure the duration of the switch bounce.Then, set up a 555 timer that outputs a square wave with a period of 1.5 times the duration of the bounce for your switch. Finally, use that timer to drive a D-flop that debounces your switch. Use one of the flops on a 74HCT74N chip. View the debounced output on your scope next to the input. How much time delay is there between the input and output signals? Make sure to tie S and R inputs HIGH (inactive). Now, get a hold of a 74HCT273N D-register. Use the output of your debounced switch to clock the register. Attach 8 logic-level input switches to the D inputs of your register. Attach LED's, or a 7 segment LED to the Q outputs of your register. Remember to tie the R reset HIGH (inactive). Experiment with your new circuit by pressing down different input buttons and then clocking your register with the debounced switch. Then, add a logic level input switch to the R reset input. This input should be normally HIGH, but should output LOW when the switch is pressed. Experiment with this Reset button. Which takes priority for the chip, the clock pulse or the reset pulse?

Although it may seem obvious to say so, we can't count unless we have some kind of memory. The Divide-by-2 Counter is the first simple counter we can make, now that we have access to memory with flip-flops.Here's the basic circuit: Let's look at what happens when we assign numbers to the voltage levels. 0 = LOW, 1 = HIGH.

To solve the problems of propagation delay introduced by the ripple counter, we'll use a synchronized counter. The synch'd counters are set up so that one clock pulse drives every stage. Since synch counters are readily available as cheap IC's, we'll move straight on to talk about how to use a counter chip.A counter chip comes with a fair number of features on it. Here's the pinout for a 74HC193, which is a 4-bit binary up/down counter with load and clear.

As we mentioned, we can chain a series of counters together to form one big counter capable of handling as many digits as we like: At what rate should the green LED blink? How can we interpret the green and red LED's as numbers? 2. Add two more stages to the Divide-by-2 counter from above, making a 3-bit ripple counter. Drive an output LED with each Q outout, and watch it count happily. Now, use a scope to watch two of the Q outputs. Expand the time axis to see the propagation delay. How much delay is there per stage? 3. Set up a synchronous counter using an SN74HC193N chip, or similar. Drive the UP and DOWN counters with straight (not-debounced) logic-level pushbutton inputs. Drive LED's from the Q-outputs. Click along with your pushbutton UP. What problems do you find using a not-debounced switch to clock the counter? 4.Add a debouncer to the UP clock. Design and build a Divide-by-5 counter, using only the SN74HC193N, and the debounced UP input. The Divide-by-5 counter should light an LED every 5th time the user has pressed the UP pushbutton. |

Comments

Post a Comment