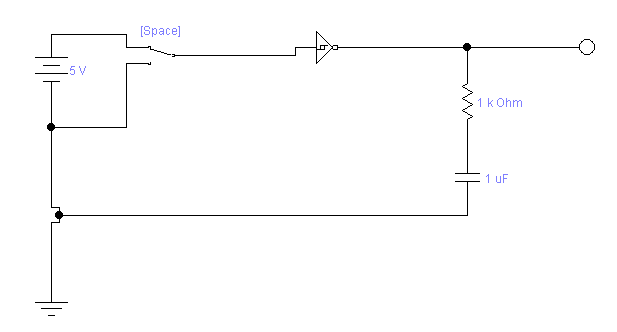

THE NOT SCHMITT TRIGGER (INVERTER)

We can try and prove the function of The Not Schmitt Gate as Clock Generator with following this Circuit Diagram in ELECTRONIC WORK BENCH And these are several information about THE NOT SCHMITT TRIGGER Schmitt Trigger Characteristic : The output is HIGH until the input rises to 66% of rail voltage. The output goes LOW when the input goes above 66%. The output remains HIGH until the input fall to 33%. A Schmitt Trigger gate can be wired as an oscillator, delay, inverter (and other functions, depending on the surrounding components). Fig: 5 shows the Schmitt Trigger wired as an oscillator , delay and inverter : Each of the 6 gates in the 74c14 can be used to create a separate "building block" and this gives the chip a wide range of capabilities. Schmitt Inverter Waveform Generator This simple waveform generator circuit consists of a single TTL 74LS14 Schmitt inverter logic gate with a capacitor, C connect...